d触发器verilog,D触发器的根本原理

D触发器(Data Trigger)是一种根本的数字电路组件,它用于存储一位二进制信息。在Verilog中,咱们能够运用以下代码来界说一个D触发器:

```verilogmodule d_flip_flop;

// 异步复位逻辑 always @ begin if q endmodule```

这段代码界说了一个名为 `d_flip_flop` 的模块,它承受三个输入:`clk`(时钟信号)、`d`(数据输入)和`reset`(异步复位信号),以及一个输出 `q`。在时钟信号的上升沿或许复位信号的上升沿,触发器会依据 `d` 的值更新 `q` 的值。假如复位信号为高,`q` 将被设置为0。

请注意,这个D触发器是一个根本的示例,它没有包含任何时序查看或归纳束缚。在实践的FPGA或ASIC规划中,或许需求增加额定的时序束缚来保证规划的时序功能。

在数字电路规划中,触发器是根本且重要的组成部分。D触发器(D Flip-Flop)作为一种根底的时序逻辑元件,广泛应用于各种数字体系中。本文将具体介绍D触发器的Verilog完成,包含其根本原理、结构以及Verilog代码编写办法。

D触发器的根本原理

D触发器是一种具有两个安稳状况的时序逻辑电路,其输出状况仅取决于当时的输入状况和时钟信号。D触发器具有以下特色:

具有一个数据输入端(D),一个时钟输入端(CLK),一个复位端(RSTN)和一个输出端(Q)。

在时钟信号的上升沿或下降沿,依据输入端D的状况改动输出端Q的状况。

复位端RSTN用于将输出端Q置为0或1,一般为低电平有用。

D触发器的结构

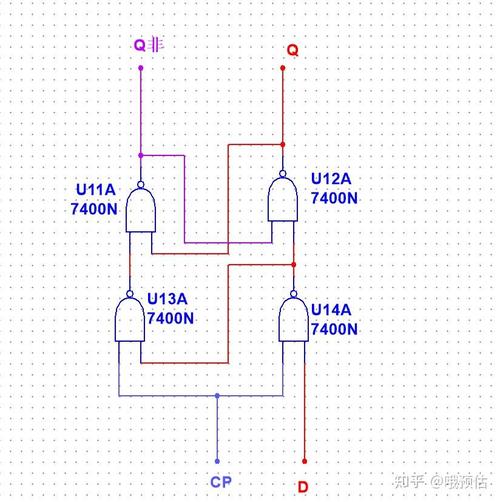

D触发器主要由一个D触发器单元和两个与非门组成。D触发器单元担任依据时钟信号和输入端D的状况改动输出端Q的状况,两个与非门别离用于完成时钟信号的上升沿触发和下降沿触发。

以下是一个D触发器的结构图:

相关

-

php和mysql,构建高效动态网站详细阅读

PHP(HypertextPreprocessor,超文本预处理器)是一种开源的服务器端脚本言语,首要用于网页开发,能够嵌入HTML中运用。PHP在网页开发中特别盛行,由于它...

2025-01-07 4

-

PHP研制工程师,技术革新下的工作开展之路详细阅读

PHP研制工程师是一个专心于运用PHP编程言语进行软件开发和体系保护的专业职位。PHP(HypertextPreprocessor)是一种广泛用于Web开发的服务器端脚本言语...

2025-01-07 3

-

女子监狱ruby,Ruby Rose的精彩演绎详细阅读

鲁比·罗丝(RubyRose)在美剧《女子监狱》(OrangeIstheNewBlack)中扮演了一个人物,引起了广泛重视。她的职业生计从音乐掌管人起步,后来做过电台...

2025-01-07 1

-

java署理形式, 署理形式概述详细阅读

署理形式(ProxyPattern)是一种规划形式,用于在不改动原始方针的基础上,为原始方针供给一个署理,以操控对这个方针的拜访。署理形式答应你增加额定的功用到现有的类,而不...

2025-01-07 3

-

python怎样翻开,新手入门攻略详细阅读

在Python中,翻开一般指的是翻开文件或网络资源。下面我会别离介绍怎样翻开文件和怎样翻开网络资源。翻开文件在Python中,你能够运用内置的`open`函数来翻开文件。...

2025-01-07 3

-

go读音,深入探讨“go”的读音及其在英语中的使用详细阅读

Go是一个英文单词,它有多种含义和用法,详细取决于上下文。在中文中,go通常被翻译为去,但这个翻译或许并不精确,由于go在英文中有更广泛的含义。例如,go能够表明...

2025-01-07 2

-

rust装备,rust装备要求详细阅读

Rust是一种体系编程言语,以其内存安全、并发性、零本钱笼统和丰厚的类型体系而出名。要装备Rust,您需求遵从以下进程:1.装置Rust:拜访Rust官方网...

2025-01-07 2

-

swift报文格局,SWIFT报文格局概述详细阅读

Swift(SocietyforWorldwideInterbankFinancialTelecommunication)是一种世界银行间电文传输体系,用于金融机构之...

2025-01-07 2

-

php开展趋势,从光辉到未来展望详细阅读

PHP的开展趋势技能方面:功用优化:PHP一向致力于进步功用,例如经过JIT编译、改善内存办理等。未来,功用优化仍然是重要方向,以应对日益杂乱的使用需求。新言语...

2025-01-07 3

-

奇特宝物go小说,实际国际的冒险之旅详细阅读

1.快眼看书:供给《奇特宝物:GO》的最新章节、全文阅览和全本TXT下载服务。这本小说情节跌宕起伏、扣人心弦,是一本情节与文笔俱佳的网游竞技小说。2.飞卢小说网:...

2025-01-07 2